## VLSI Architectures for the Forward-Backward Algorithm

by

### **Warren Jeffrey Gross**

A Thesis submitted in conformity with the requirements for the degree of Master of Applied Science, Department of Electrical and Computer Engineering, University of Toronto

© Copyright by Warren Jeffrey Gross 1999

## National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-45609-9

#### VLSI Architectures for the Forward-Backward Algorithm

Warren Jeffrey Gross

Master of Applied Science, 1999

Department of Electrical and Computer Engineering

University of Toronto

### Abstract

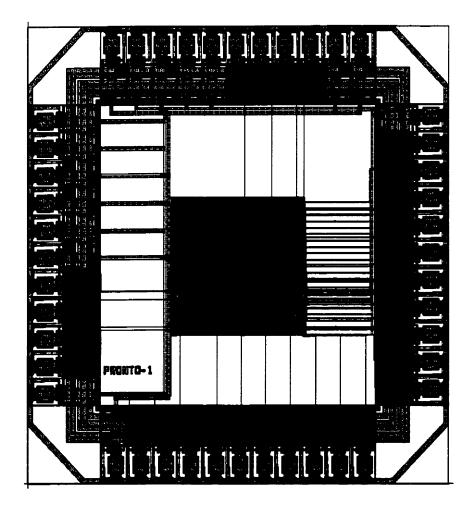

The forward-backward algorithm, also known as the BCJR or MAP algorithm, is a detection algorithm that provides soft reliability estimates. This thesis discusses issues relevant to the practical implementation of the forward-backward algorithm. Two applications are chosen for more detailed study: (i) turbo decoding and (ii) soft-output detection of class-IV partial response signalling. A novel circuit is introduced that eliminates the need for a lookup table in the computational kernel of the forward-backward algorithm. The design and implementation of an FPGA-based turbo decoder is presented. The difference-metric forward-backward algorithm is derived for class-IV partial response signalling. A test chip was designed in a 0.5  $\mu$ m CMOS process and is expected to operate at speeds greater than 120 Mbps. The core area is 0.81 mm<sup>2</sup> and the overall silicon area is 7.3 mm<sup>2</sup>.

### Acknowledgments

This thesis would not have been possible without the help of many people and organizations. I would like to use this space to make special mention of my advisor, colleagues, friends and family who helped me towards my goals.

I wish to thank my advisor Professor Glenn Gulak for his support, ideas and encouragement throughout the course of this work. I hope to continue my collaboration with him in the future.

Financial support from NSERC as well as fabrication support from CMC are greatly appreciated.

I also wish to thank Professors Frank Kschischang, Emmanuel Boutillon, Amir Banihashemi and Saeed Gazor for their enlightening discussions.

Special mention goes out to Vincent Gaudet for the work which we did together on PRONTO and the interleaver project. Also, thanks to Jason Podaima for helping with the place and route of the PRONTO-1 chip.

Thanks to Dave, Marcus, Jaro and Peter for putting up with all my questions about the CAD tools.

I would like to thank all of my colleagues in the Communications Algorithms Laboratory at the U. of T.

Thanks to all my friends in LP392: Ali, Andy, Jason A., Javad, Jeff, Jordan, Ken, Khalid, Mark, Nirmal, Qiang, Rob, Sandy, Tooraj, Vaughn, Wai Ming and Yaska.

I am extremely grateful to my parents for their love, support and encouragement.

"Now it is a strange thing, but things that are good to have and days that are good to spend are soon told about, and not much to listen to; while things that are uncomfortable, palpitating, and even gruesome, may make a good tale, and take a deal of telling anyway."

J. R. R. Tolkien, The Hobbit

## Contents

| CHAPTE | <b>R</b> 1                                    | Introduction                                                                                                                                                      | 1              |

|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.1    | Moti                                          | vation                                                                                                                                                            | 1              |

| 1.2    | Obje                                          | ctives                                                                                                                                                            | 2              |

| 1.3    | Orga                                          | anization of the Thesis                                                                                                                                           | 2              |

| CHAPTE | R 2                                           | The Forward-Backward Algorithm                                                                                                                                    | 3              |

| 2.1    | <b>2.1.1</b>                                  | ction in the Presence of Noise<br>The Maximum A-Posteriori and Maximum Likelihood Rules<br>Sequence Detection and the Viterbi Algorithm                           | 4              |

| 2.2    | $\begin{array}{c} 2.2.1 \\ 2.2.2 \end{array}$ | Forward-Backward Algorithm<br>Soft-Output Algorithms<br>Description of the Forward-Backward Algorithm<br>The Forward-Backward Algorithm in the Logarithmic Domain | 7<br>9         |

| 2.3    | The                                           | Sliding Window Forward-Backward Algorithm                                                                                                                         | 12             |

| 2.4    | Sum                                           | mary                                                                                                                                                              | 1 <del>9</del> |

| СНАРТЕ | <b>R</b> 3                                    | Implementation of a Turbo Decoder                                                                                                                                 | 20             |

| 3.1    | Turt                                          | oo Codes                                                                                                                                                          | 20             |

|        |                                               | Concatenated Codes                                                                                                                                                |                |

|        |                                               | Encoders for Turbo Codes                                                                                                                                          |                |

|        |                                               | Interleavers for Turbo Codes                                                                                                                                      |                |

|        | 3.1.4                                         | The Iterative Decoding Algorithm                                                                                                                                  | 23             |

| 3.2    | Prev                                          | rious Turbo Decoder Implementations                                                                                                                               | 24             |

|        | 3.2.1                                         | CAS5093 [Comatlas95]                                                                                                                                              | 25             |

|        | 3.2.2                                         | TURBO4 [BCPT95]                                                                                                                                                   | 25             |

|        | 3.2.3                                         | JPL FPGA [JPL1997][BDMP97]                                                                                                                                        | 25             |

|        | 3.2.4                                         | University of Dresden FPGA [Koora98]                                                                                                                              | 25             |

|        |                                               | University of South Australia FPGA [Pietrobon98]                                                                                                                  |                |

|        | 3.2.6                                         | University of Michigan ASIC [HYS98]                                                                                                                               | 25             |

|        | 3.2.7                                         | University of California San Diego FPGA [HOCS98]                                                                                                                  | 26             |

|        | 3.2.8                                         | Communications Research Centre Software [CRC98]                                                                                                                   | 26             |

| 33     | Dosi                                          | gn of a Hardware-Ready Turbo Decoder                                                                                                                              | 27             |

| 0.0    | 331                                           | Simulation of the Turbo Code                                                                                                                                      | $\frac{1}{27}$ |

|        |                                               | Approximating the Channel SNR                                                                                                                                     |                |

|        |                                               | Fixed-Point Turbo Decoding                                                                                                                                        |                |

| 3.4    | TOR                                           | BO-TM2: An FPGA Implementation                                                                                                                                    | 34             |

|        |                                               | The Transmogrifier-2 (TM-2)                                                                                                                                       |                |

|        |                                               | System Architecture                                                                                                                                               |                |

|        |                                               | Interface to the SUN Workstation                                                                                                                                  |                |

|        |                                               | Memory Controller                                                                                                                                                 |                |

| 3.4.5      | Datapath                                                                                      |    |

|------------|-----------------------------------------------------------------------------------------------|----|

| 3.4.6      | Control Unit                                                                                  |    |

| 3.4.7      | Logic Synthesis and Performance                                                               |    |

| 3.5 Sum    | mary                                                                                          |    |

| CHAPTER 4  | A Soft-Output Partial Response Detector                                                       | 45 |

|            |                                                                                               | 45 |

|            | ial Response for Magnetic Recording<br>Class-IV Partial Response for Magnetic Recording (PR4) |    |

|            | The Difference Metric Viterbi Algorithm                                                       |    |

|            |                                                                                               |    |

|            | Difference Metric Forward-Backward Algorithm                                                  |    |

|            | Motivation<br>Derivation of the Algorithm                                                     |    |

|            | Initialization                                                                                |    |

|            | Normalization and Overflow                                                                    |    |

|            | Summary of the DMFB for Class-IV Partial Response                                             |    |

|            | -                                                                                             |    |

|            | Architectures for Class-IV Partial Response                                                   |    |

|            | The Limiter Form of the DMFB: MAX-DMFB<br>Eliminating the Noise Variance Problem              |    |

|            | The Sliding Window Architecture                                                               |    |

|            | 5                                                                                             |    |

|            | NTO-1: An ASIC Implementation                                                                 |    |

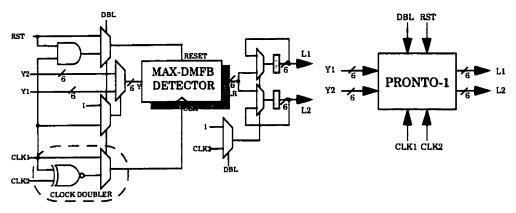

|            | MAX-DMFB Detector Architecture                                                                |    |

|            | Control Unit                                                                                  |    |

|            | Limiter<br>Adders                                                                             |    |

|            | Clock Doubler                                                                                 |    |

|            | Test Chip Synthesis and Layout                                                                |    |

|            | mary                                                                                          |    |

| 4.5 5011   | mary                                                                                          |    |

| CHAPTER 5  | Conclusions                                                                                   | 65 |

| 5.1 Sum    | mary and Conclusions                                                                          | 65 |

| 5.2 Cont   | ributions of this Thesis                                                                      |    |

| 5.3 Suga   | estions for Future Research                                                                   |    |

|            | Serial and hybrid concatenated codes                                                          |    |

|            | Interleaver design                                                                            |    |

|            | Very high speed DSP or microprocessor turbo decoder                                           |    |

|            | Hardware variance estimation                                                                  |    |

|            | Continuous time turbo decoding on the TM-2                                                    |    |

| 5.3.6      | Turbo decoder ASIC                                                                            | 67 |

| APPENDIX A | TORBO-TM2 FB Algorithm                                                                        | 68 |

| References |                                                                                               | 71 |

# **List of Figures**

| 2-1 The basic digital communication system                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-2 Position of the memory in an ISI channel (a) and a convolutional coding scheme (b)5                                                                                                                                                                                                                                  |

| <b>2-3</b> A convolutional rate $R = 1/2$ encoder with memory length $v = 2$                                                                                                                                                                                                                                             |

| 2-4 A state transition diagram for the convolutional encoder shown in Fig. 2-3                                                                                                                                                                                                                                           |

| <b>2-5</b> A 3 stage trellis diagram corresponding to the encoder of Fig. 2-3 and the state diagram of Fig. 2-4. The highlighted path corresponds to a message sequence of {1,0,1} given the starting state 01                                                                                                           |

| <b>2-6</b> The forward recursion in the Viterbi algorithm7                                                                                                                                                                                                                                                               |

| 2-7 Trellis processing in an $N = 5$ stage 4-state Forward-Backward algorithm corresponding<br>to the encoder of Fig. 2-3. Shown is the calculation of one particular term in the lower sum-<br>mation of Equation 2-11. The terms in the upper summation are dashed while the terms in<br>the lower summation are solid |

| <b>2-8</b> Log-domain processing in the forward recursive equation. Multiplications become addi-<br>tions and additions become the MAX <sup>*</sup> operation. The shaded components are removed for the<br>approximate algorithm                                                                                        |

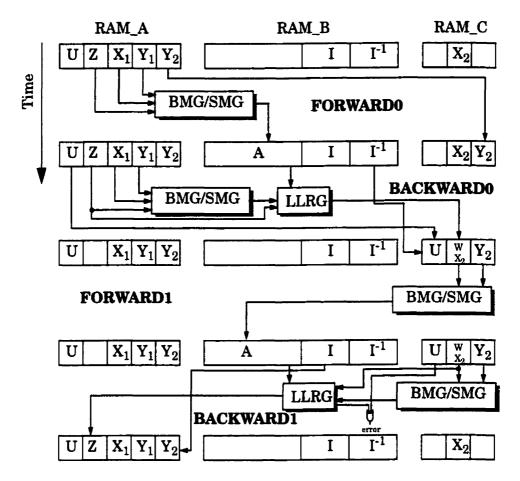

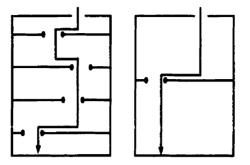

| <b>2-9</b> The log-domain sliding window Forward-Backward algorithm for $M_b = 1$ [DawidM95].<br>The shaded boxes represent memory storage. The branch metric generators are not shown.<br>14                                                                                                                            |

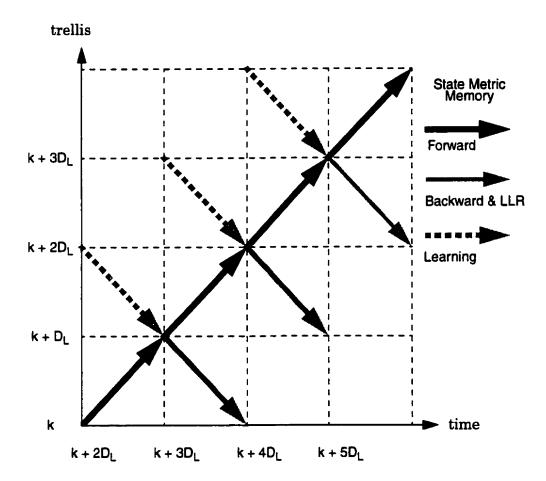

| <b>2-10</b> Space-time diagram for the sliding window Forward-Backward algorithm with $M_b = D_L$ [DawidM95]. The shaded areas represent the memory for the forward state metrics 14                                                                                                                                     |

| <b>2-11</b> A snapshot of computation in the trellis15                                                                                                                                                                                                                                                                   |

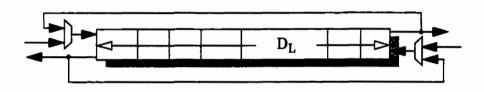

| <b>2-12</b> Architecture of the sliding-window Forward-Backward algorithm with $M_b=D_L$ (derived from [DawidM95])                                                                                                                                                                                                       |

| <b>2-13</b> Implementing the forward state metric memory with a bi-directional shift register. In<br>(a) results from trellis block i are stored while results from the previous block i - 1 are sent to<br>the soft output unit. In (b) results from block i + 1 are stored while the previously stored block           |

| i is read out in the opposite order in which it was written | 17 |

|-------------------------------------------------------------|----|

|-------------------------------------------------------------|----|

**2-15** Pseudo-code for the sliding window algorithm.  $\{A\}$  are the forward state metrics,  $\{B\}$  are the backward state metrics and  $\{B_{learn}\}$  are the backward state metrics in the learning recursion. The state metric processing elements are represented by smg() and the branch metric generators by bmg(). The soft output unit is represented by soft\_output(). The forward state metrics are stored in SM\_MEM. The soft output is LLR. Two assignment operators (:=) on the same line imply simultaneous assignment.

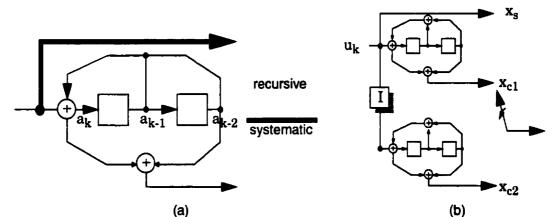

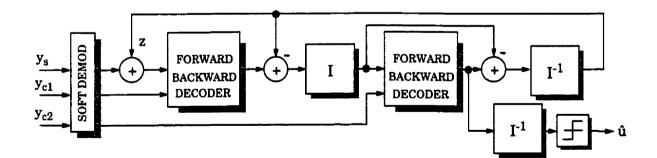

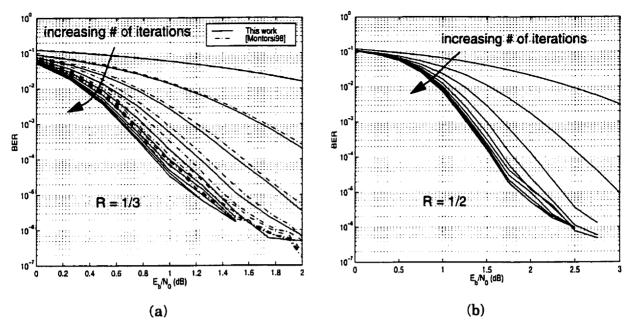

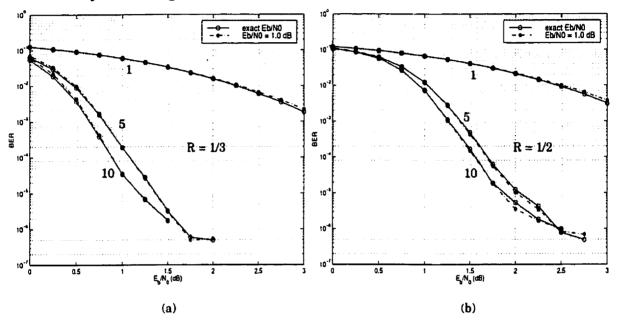

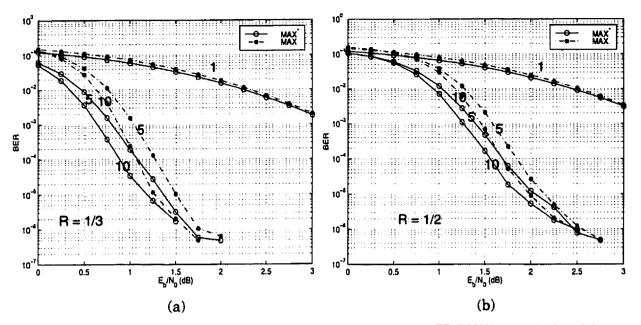

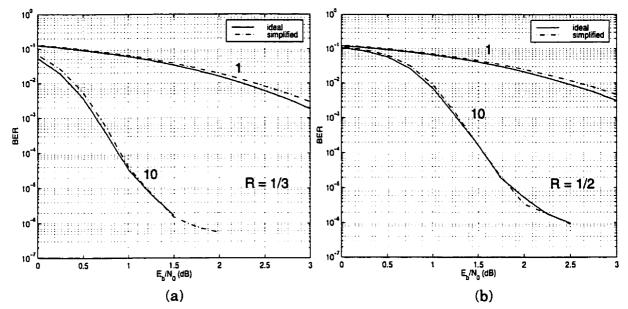

**3-5** 4-state turbo code performance. Interleaver length 1024. (a) rate 1/3. (b) rate 1/2 ..... 28

3-7 Approximation of the noise variance in the soft demodulator. Shown are iterations 1,5 and

| 3-11 Simplified MAX* circuit                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3-12</b> Performance of the simplified hardware-ready turbo decoder compared to the ideal float-<br>ing point turbo decoder. 4-state turbo code, interleaver length 1024. 1 and 10 iterations<br>shown. (a) rate 1/3. (b) rate 1/2                            |

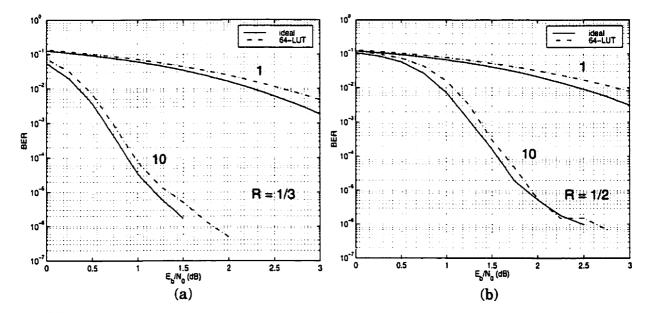

| <b>3-13</b> Effect of implementing the soft demodulator after the A/D converter as a 64 x 6 LUT compared with the ideal floating point turbo decoder. 4-state turbo code, interleaver length 1024. 1 and 10 iterations shown. (a) rate 1/3. (b) rate 1/2         |

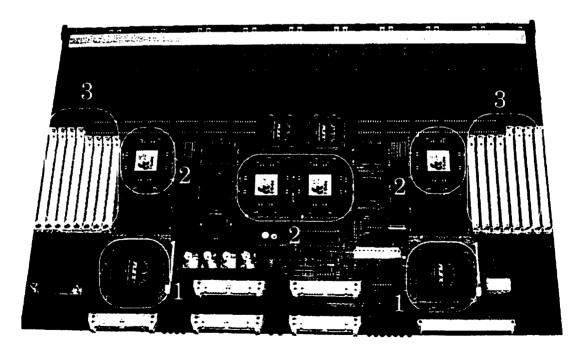

| <b>3-14</b> Photograph of one board of the TM-2. 1. Altera 10k50 FPGAs. 2. I-Cube crossbar switches. 3. SRAM banks (unpopulated)                                                                                                                                 |

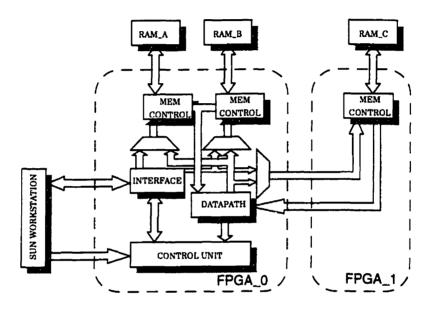

| <b>3-15</b> TORBO-TM2 system architecture                                                                                                                                                                                                                        |

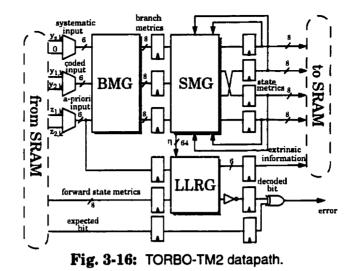

| <b>3-16</b> TORBO-TM2 datapath                                                                                                                                                                                                                                   |

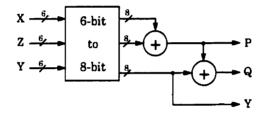

| <b>3-17</b> Branch Metric Generator (BMG). X is the systematic input, Y is the coded input and Z is the a-priori information input                                                                                                                               |

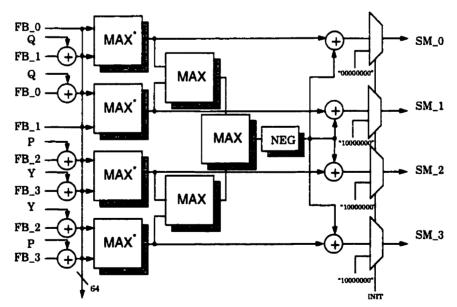

| <b>3-18</b> State Metric Generator (SMG). FB_i are the values of the previous state metrics from the feedback path. The INIT signal selects the initial state metrics. SM_i are the new state metrics. All values not otherwise indicated are 8 bits             |

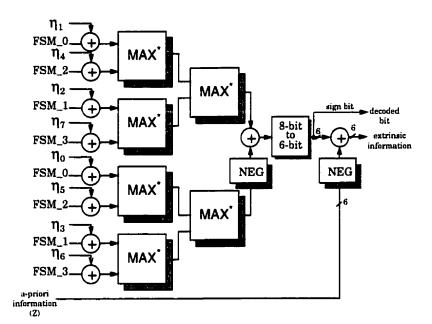

| <b>3-19</b> Log-likelihood Ratio Generator (LLRG). FSM_i are the forward state metrics recalled from SRAM. $\eta_i$ are the sum of the backward state metrics and the branch metrics as described in Appendix A. All values are 8-bit unless otherwise indicated |

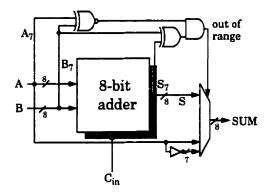

| <b>3-20</b> 8-bit saturating adder. $SUM = A+B$ if the result can be represented in the 8-bit format otherwise $SUM = 01111111$ (most positive number) or 10000000 (most negative number).40                                                                     |

| 3-21 TORBO-TM2 memory schedule                                                                                                                                                                                                                                   |

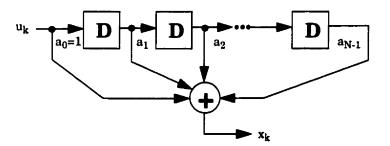

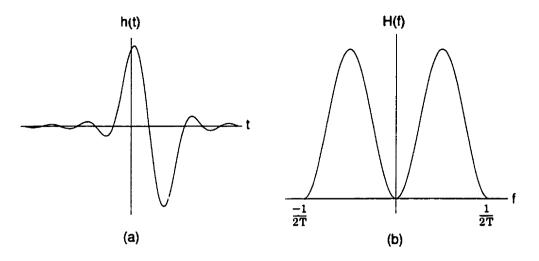

| <b>4-1</b> The general structure of an FIR filter that models the partial response transfer function of Equation 4-1                                                                                                                                             |

| 4-2 PR4 impulse response (a) and frequency response (b)                                                                                                                                                                                                          |

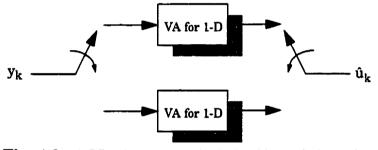

| <b>4-3</b> A PR4 decoder can be built with two independent time-interleaved 1-D decoders. The Viterbi decoders are clocked at 1/2 the channel rate                                                                                                               |

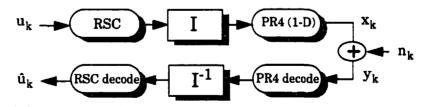

| 4-4 Concatenating a convolutional code with PR4 signalling. The information shared between                                                                                                                                                                       |

| the two decoders c | in either be hard | or soft4 | 8 |

|--------------------|-------------------|----------|---|

|--------------------|-------------------|----------|---|

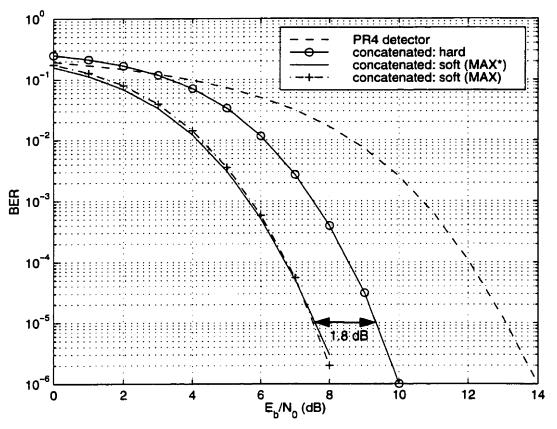

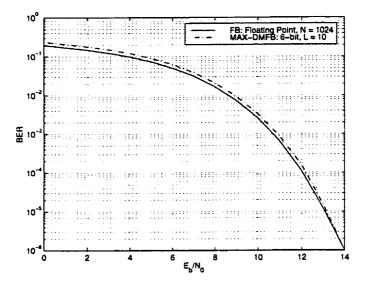

| <b>4-5</b> Bit-error rate performance of a serial concatenation of a 4-state 7/5 RSC with PR4.The blocksize is 1K bits. A soft PR4 detector provides 1.8 dB of gain over a hard output detector at a BER of 10 <sup>-5</sup> . The approximate forward-backward algorithm using MAX as the arithmetic kernel performs nearly as well as the optimum MAX <sup>*</sup> algorithm |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>4-6</b> The partial response system with transfer function $F(D) = 1 + \rho D$                                                                                                                                                                                                                                                                                              |

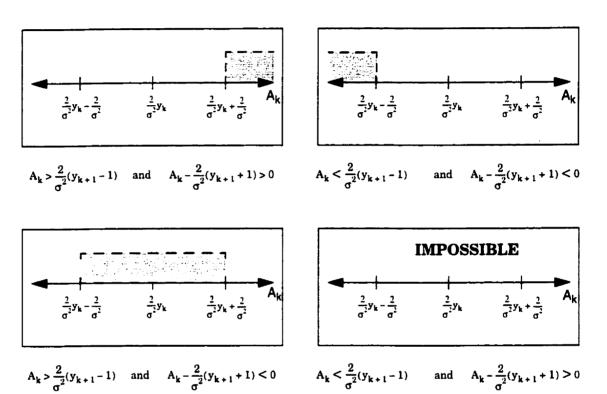

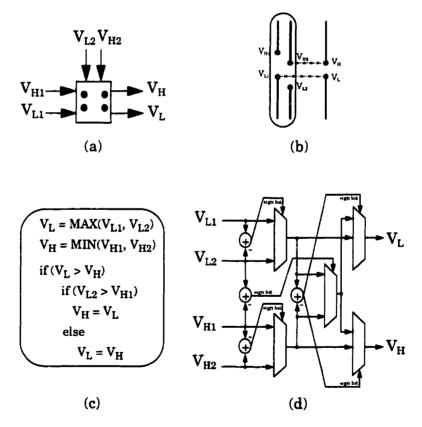

| 4-7 The possible combinations of inputs to the forward recursion equation55                                                                                                                                                                                                                                                                                                    |

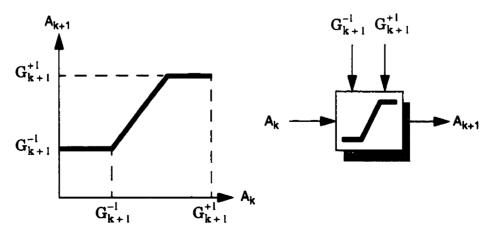

| 4-8 The limiter used as the update rule for the forward recursion equation55                                                                                                                                                                                                                                                                                                   |

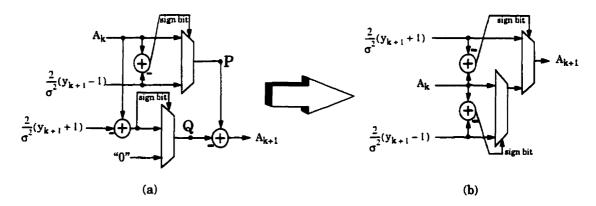

| 4-9 A limiter saves an adder in the critical path of the recursion hardware                                                                                                                                                                                                                                                                                                    |

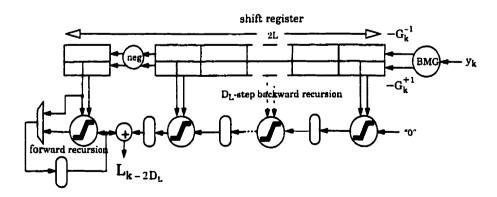

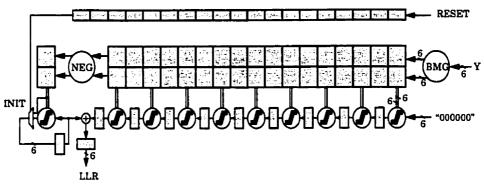

| <b>4-10</b> The sliding window MAX-DMFB for $M_b = 1$                                                                                                                                                                                                                                                                                                                          |

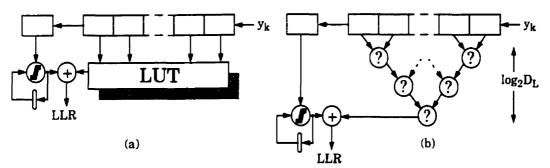

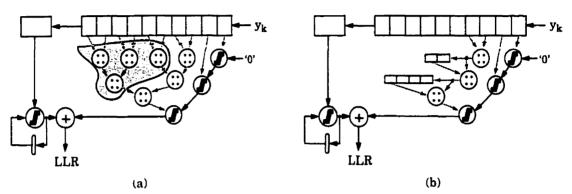

| 4-11 Parallel processing of the backward recursion using (a) a lookup table or (b) A tree. 58                                                                                                                                                                                                                                                                                  |

| <b>4-12</b> A graphical analogy to a chain of limiters. The chain can be replaced by a single limiter which has the same overall effect                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                |

| <b>4-13</b> The Interval Adjustment Unit (IAU). (a) Symbol. (b) Example of IAU operation. (c) Algorithm. (d) Hardware implementation                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                |

| gorithm. (d) Hardware implementation                                                                                                                                                                                                                                                                                                                                           |

| gorithm. (d) Hardware implementation                                                                                                                                                                                                                                                                                                                                           |

| gorithm. (d) Hardware implementation                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>gorithm. (d) Hardware implementation</li></ul>                                                                                                                                                                                                                                                                                                                        |

# **List of Tables**

| 3-1 | Summary of Turbo Decoder Implementations                                | . 26 |

|-----|-------------------------------------------------------------------------|------|

| 3-2 | TORBO-TM2 I/O parameters.                                               | . 35 |

| 3-3 | I/O signals to the interface unit.                                      | . 37 |

| 3-4 | Speed and area of the saturating adder using different component adders | . 38 |

| 3-5 | Variables involved in the memory schedule for TORBO-TM2                 | . 41 |

| 4-1 | PRONTO-1 specifications.                                                | . 64 |

# List of Symbols

| $\alpha_k(s)$                                     | Forward state probability at state s and time k                         |

|---------------------------------------------------|-------------------------------------------------------------------------|

| $\beta_{k-l}(s)$                                  | Backward state probability at state s and time k                        |

| $\gamma_k(s'\!,s)$                                | Branch probability between states s' and s at time k                    |

| $\Delta_{\mathbf{k}}$                             | Difference metric                                                       |

| $\eta_k(s',s)$                                    | Sum of backward state metrics and branch metrics at time k              |

| v                                                 | Memory length of encoder or intersymbol interference channel            |

| ρ                                                 | Weight of the delayed input to the adder in a PR4 filter                |

| $\sigma^2$                                        | Noise variance                                                          |

| a <sub>k</sub>                                    | Shift register input                                                    |

| A <sub>k</sub>                                    | Forward difference metric                                               |

| A <sub>k</sub> (s)                                | Forward state metric at state s and time k                              |

| B <sub>k</sub>                                    | Backward difference metric                                              |

| $B_k(s)$                                          | Backward state metric at state s and time k                             |

| $\mathbf{c}_{\mathbf{k}}(\mathbf{s}',\mathbf{s})$ | Expected symbol along the branch from state $s'$ to state $s$           |

| D                                                 | Unit delay                                                              |

| DL                                                | Learning period                                                         |

| E <sub>b</sub> /N <sub>0</sub>                    | Bit energy-to-noise density ratio                                       |

| f                                                 | Turbo decoder clock speed in Hz                                         |

| $f_{\bm{y}}(\bm{y})$                              | Likelihood function.                                                    |

| $G_{k+1}^{-i}, G_{k+1}^{+i}$                      | Branch metrics for the log-difference-metric forward-backward algorithm |

| $G_k(s',s)$                                       | Branch metric between states s' and s at time k                         |

| I                 | Interleaver                                                |

|-------------------|------------------------------------------------------------|

| I <sup>-1</sup>   | Deinterleaver                                              |

| k                 | Time index                                                 |

| L(u)              | Log-likelihood ratio corresponding to transmitted symbol u |

| M <sub>b</sub>    | Number of symbols decoded per learning recursion           |

| MAX               | Maximum operator                                           |

| MAX <sup>*</sup>  | Maximum adjusted by a correction factor                    |

| n <sub>k</sub>    | AWGN noise sample                                          |

| N                 | Block length                                               |

| P(u y)            | A-posteriori probability                                   |

| $P_e(u, y)$       | Probability of symbol error                                |

| R                 | Rate                                                       |

| s                 | Present state                                              |

| s'                | Predecessor state                                          |

| S                 | Number of states                                           |

| Т                 | Symbol period                                              |

| û <sub>k</sub>    | Information bit                                            |

| W <sub>k</sub>    | Extrinsic information                                      |

| WL                | Wordlength                                                 |

| WLI               | Number of integer bits in a fixed point word               |

| $WL_F$            | Number of fractional bits in a fixed point word            |

| x <sub>s,k</sub>  | Systematic output of a turbo encoder                       |

| x <sub>c1,k</sub> | First coded output of a turbo encoder                      |

| x <sub>c2,k</sub>         | Second coded output of a turbo encoder                      |

|---------------------------|-------------------------------------------------------------|

| <b>x</b> k                | Modulated symbol                                            |

| y <sub>s,k</sub>          | Received systematic value at the input of a turbo decoder   |

| y <sub>cl,k</sub>         | Received first coded value at the input of a turbo decoder  |

| У <sub>c2,k</sub>         | Received second coded value at the input of a turbo decoder |

| $\mathbf{y}_{\mathbf{k}}$ | Received symbol                                             |

| z                         | A-priori information                                        |

## **List of Acronyms**

| ACS        | Add-Compare-Select                                                                       |

|------------|------------------------------------------------------------------------------------------|

| APP        | A-Posteriori Probability                                                                 |

| AWGN       | Additive White Gaussian Noise                                                            |

| BCJR       | Bahl, Cocke, Jelinek and Raviv                                                           |

| BER        | Bit Error Rate                                                                           |

| CCS        | Compare-Compare-Select                                                                   |

| DMFB       | Difference-Metric Forward-Backward algorithm                                             |

| DMVA       | Difference-Metric Viterbi Algorithm                                                      |

| FB         | Forward-backward algorithm                                                               |

| FPGA       | Field Programmable Gate Array                                                            |

| IAU        | Interval Adjustment Unit                                                                 |

| ISI        | Intersymbol Interference                                                                 |

| log-FB     | Forward-Backward algorithm in the logarithmic domain                                     |

| log-ML     | Maximum Likelihood rule in the logarithmic domain                                        |

| max-log-FB | Forward-Backward algorithm in the log domain using MAX instead of $\operatorname{MAX}^*$ |

| MAP        | Maximum-A-Posteriori                                                                     |

| MAX-DMFB   | Difference-Metric Forward-Backward algorithm using MAX instead of $MAX^*$                |

| ML         | Maximum Likelihood                                                                       |

| PR4        | Class-IV Partial Response                                                                |

| RSC        | Recursive Systematic Convolutional code                                                  |

| SOVA       | Soft Output Viterbi Algorithm                                                            |

|            |                                                                                          |

### SNR Signal-to-Noise Ratio

TM-2 The Transmogrifier-2 field programmable system

Chapter

## Introduction

### 1.1 Motivation

Error correcting codes in digital communications permit reliable transmission of data in noisy channels. The idea is to transmit some extra information along with the original message that in some way describes the intended message. The relationship between the extra and original information is known and can be exploited in the decoder to make reliable bit decisions.

Turbo codes, introduced in 1993 [BGT93] are the best known error correcting codes with a practical decoding algorithm. They have bit error rate performance close to the Shannon limit. The heuristic iterative decoding algorithm provides remarkable results at a very low complexity compared to codes with similar performance. In recent years, researchers have made a lot of progress in understanding these codes and in suggesting many promising applications. The focus of the research is now starting to turn towards practical hardware implementation issues.

The main component of a turbo decoder is the forward-backward algorithm. The forwardbackward algorithm differs from the well-known Viterbi algorithm in that it provides 'soft' information about the reliability of each bit that it decodes. This soft information can be used in a subsequent use of the algorithm to improve its initial estimate. Although known for about thirty years, the forward-backward algorithm developed an undeserved reputation as being too difficult to implement. Even if it could be simplified somewhat, it was unlikely to beat the Viterbi algorithm for simplicity and there was no compelling need for soft outputs. The focus has suddenly shifted to the forward-backward algorithm as it provides optimal symbol-by-symbol soft outputs for turbo decoders. Initial implementations of turbo decoders used the SOVA algorithm, a soft-output variant of the Viterbi algorithm that was less complex than the forward-backward algorithm but did not provide optimum soft outputs. It would be interesting to design a turbo decoder using the forward-backward algorithm and address the implementation issues.

Another interesting area is the detection of signals in magnetic recording. The principles of detection are similar to error correcting coding: the correlation between transmitted signals is known and can be exploited in the receiver. A standard technique for detecting one of the popular signalling schemes, class-IV partial response, is called the difference metric Viterbi algorithm. Are soft outputs useful for this type of system? If so, can an analogous difference metric forward-backward algorithm be derived to compete with the difference metric Viterbi algorithm?

### **1.2 Objectives**

The objective of this thesis is to present examples of practical implementations of the forward backward algorithm and to propose suitable VLSI architectures. Specifically, we have chosen to implement a turbo decoder and a detector for class-IV partial response signalling.

### **1.3 Organization of the Thesis**

This thesis contains five chapters and one appendix. Chapter 2 is a review of the forwardbackward algorithm and simplifications for its practical implementation. Chapter 3 presents the design of a turbo decoder for the reconfigurable TM-2 FPGA system. Chapter 4 describes the design and implementation of a soft-output decoder for class-IV partial response. Chapter 5 is a summary of the work and makes some suggestions for future research. Appendix A is a detailed listing of the equations of the forward-backward algorithm used to implement the turbo decoder in Chapter 3.

# 2

Chapter

## The Forward-Backward Algorithm

The forward-backward algorithm is a detection algorithm that provides reliability estimates for each symbol that it decodes. Virtually ignored for many years because of its perceived complexity, interest in this algorithm has been reignited by the recent discovery of turbo codes. This chapter is a review of the forward-backward algorithm and techniques for its practical implementation. Section 2.1 defines the problem which the rest of the thesis is dedicated to solving: extracting the intended message from a noisy signal. A solution to this problem, the forward-backward algorithm is described in Section 2.2. A practical method for implementing the forward-backward algorithm is presented in Section 2.3. The main points of this chapter are summarized in Section 2.4.

### 2.1 Detection in the Presence of Noise

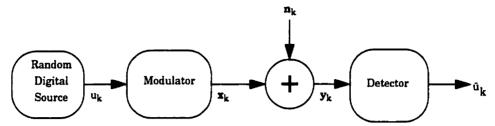

Signal *detection* is the attempt to recover a discrete-valued transmitted signal that has been corrupted by noise. In this thesis, we are only concerned with a discrete-time system and therefore will consider time in intervals of T seconds where T is called the symbol period. Fig. 2-1 is a block diagram of a basic digital communication system. The messages to be transmitted are equally likely binary symbols  $u_k$  where the subscript k refers to the time index. After transmission through an Additive White Gaussian Noise (AWGN) channel the input at the receiver,  $y_k$  is the sum of a noise sample and the modulated signal  $x_k$ :

$$\mathbf{y}_{\mathbf{k}} = \mathbf{x}_{\mathbf{k}} + \mathbf{n}_{\mathbf{k}} \tag{2-1}$$

The detector is a combined demodulator and symbol estimator that gives estimates  $\hat{u}_k$  of the original message symbols.

Fig. 2-1: The basic digital communication system.

### 2.1.1 The Maximum A-Posteriori and Maximum Likelihood Rules

The best possible detector is one that makes the fewest errors in estimating the message symbols. In other words, an optimum detector minimizes the probability of symbol error [Haykin88]:

$$P_{e}(\mathbf{u}, \mathbf{y}) = 1 - P(\mathbf{u}|\mathbf{y})$$

(2-2)

As seen in the above equation, this is equivalent to maximizing P(u|y). This quantity is called the *a*-posteriori probability and is the probability of the information symbol given that the noisy value has been received. A maximum-a-posteriori (MAP) decision rule can be implemented by calculating the a-posteriori probabilities of the two possible message symbols and then choosing symbol u (0 or 1) that results in the largest. Using Bayes' rule on Equation 2-2 we can write:

$$P(\mathbf{u}|\mathbf{y}) = \frac{P(\mathbf{u})f_{\mathbf{y}}(\mathbf{y}|\mathbf{u})}{f_{\mathbf{y}}(\mathbf{y})}$$

(2-3)

where  $f_{\mathbf{y}}(\mathbf{y}|\mathbf{u})$  is called the *likelihood function*. If the message symbols are equally likely then the MAP rule reduces to finding the message symbol that maximizes the likelihood function. It is often more convenient to apply the *maximum-likelihood* (ML) rule in the log domain by maximizing the logarithm of the likelihood function.

### 2.1.2 Sequence Detection and the Viterbi Algorithm

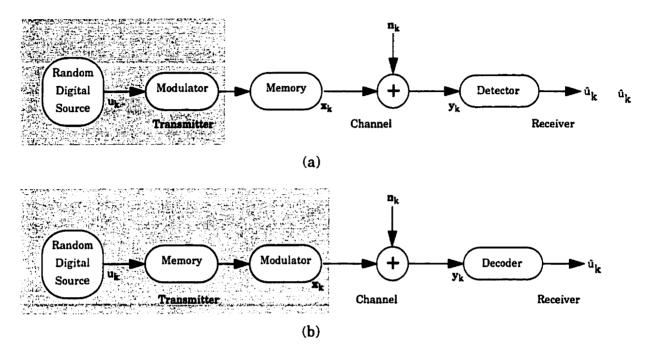

The error performance of the system can be improved if a constraint is imposed on the sequence of transmitted symbols. A channel in which the transmitted symbols are dependent on the past history of transmitted symbols is said to have *memory*. The channel memory can be naturally present or explicitly inserted. One example of a channel with

memory is an *intersymbol interference* (ISI) channel. Convolutional coding involves inserting memory in the transmitter. Fig. 2-2 shows the different positions of the memory between the two techniques. Regardless of the source of the memory, the detector can use the constraint imposed on the received symbols to make more intelligent decisions. Convolutional codes will be described in greater detail in Chapter 3 while Chapter 4 deals with intersymbol interference channels.

Fig. 2-2: Position of the memory in an ISI channel (a) and a convolutional coding scheme (b).

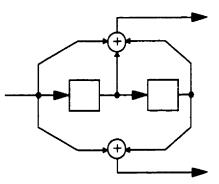

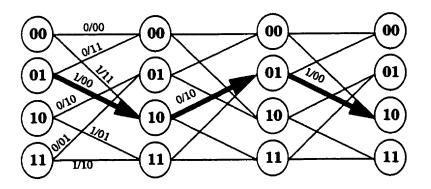

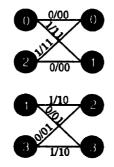

Consider the shift register structure in Fig. 2-3, which is the encoder for a convolutional code with a memory length (v) of two. We say the *rate* (R) of the code is 1/2 since there are two output bits for every input bit. The *state* of the encoder at a given time is defined by the contents of the shift register. For example, the v = 2 shift register shown here has four possible states, namely "00", "01", "10" and "11". A state machine diagram which shows the valid state transitions is shown in Fig. 2-4. The edges of the diagram are labelled with the input bit / output bits. A more convenient representation can be derived by adding a time axis. Each path from the left hand side through the right hand side of the resulting *trellis* diagram in Fig. 2-5 corresponds to a unique transmitted sequence of bits.

The problem of detection (which we will call decoding in the case of a convolutional code) can now be cast in terms of operations on the trellis. The well-known Viterbi algorithm (VA) [Viterbi67][Omura69][Forney73] is an application of dynamic programming to digital

Fig. 2-3: A convolutional rate R = 1/2 encoder with memory length v = 2.

Fig. 2-4: A state transition diagram for the convolutional encoder shown in Fig. 2-3.

**Fig. 2-5:** A 3 stage trellis diagram corresponding to the encoder of Fig. 2-3 and the state diagram of Fig. 2-4. The highlighted path corresponds to a message sequence of  $\{1,0,1\}$  given the starting state 01

communications that operates on a trellis. If the edges (branches) in the trellis are labelled with a number that is proportional to the probability of that branch being taken, then the path with the largest accumulated number will be the most likely path to have occurred. In practice, the negative likelihood function is used instead, which reformulates the problem to finding the minimum length path through the trellis. For an AWGN channel, a *branch metric* is simply the Euclidean distance between the received and expected transmitted symbols. Therefore, the Viterbi algorithm, in choosing the sequence with the lowest accumulated metric, performs maximum likelihood sequence detection. The key to the algorithm is the observation that at time k the shortest path must contain the shortest path up to time k-1 and therefore the other paths leading up to time k-1 can be thrown away. The procedure consists of two steps. In the first step, the accumulated metrics are calculated in the direction of increasing time in a *forward* recursion through the trellis. The accumulated metrics, called *forward state metrics* are calculated at each state at time k as

$$A_{k}(s) = \min_{s'} (G_{k}(s', s) + A_{k-1}(s'))$$

(2-4)

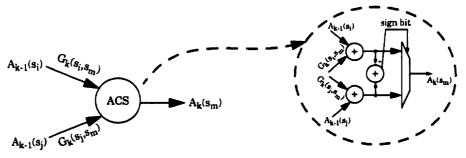

where  $A_k(s)$  is the forward state metric at state s at the current time interval,  $A_{k-1}(s')$  is the forward state metric at a predecessor state s' at the previous time interval and  $G_k(s', s)$ is the branch metric associated with the branch between states s' and s. The computational kernel of Equation 2-4 which is the critical path of the algorithm is the so-called Add Compare Select (ACS) operation (see Fig. 2-6). In the second step, the shortest path is determined by tracing back through the trellis according to the decisions made at each time interval by the forward recursion. Using the fact that competing paths are likely to have merged into the shortest path at about 5v time intervals back from the current time [ClarkC81], a practical real-time implementation can be built using a finite amount of memory. The two methods for performing traceback are the *register exchange* method and the *pointer traceback* method. The reader is directed to [ClarkC81][Rader81][FeyginG91] for descriptions of how to implement the two traceback methods.

Fig. 2-6: The forward recursion in the Viterbi algorithm.

### 2.2 The Forward-Backward Algorithm

### 2.2.1 Soft-Output Algorithms

It can be useful for a decoding algorithm to provide an estimate of the reliability of the decoded bits. The 'soft' reliability values can be used in some way to adjust the decoding algorithm to provide better performance. As far back as 1973, Forney proposed the use of

'augmented outputs' from the Viterbi algorithm as a measure of reliability of the decoding process [Forney 73]. Forney's heuristic idea to use the difference in state metrics between the best path and the next shortest path led to the soft-output Viterbi algorithm described by Batail [Battail87] and Hagenauer and Hoeher [HagenauerH89].

It is important to define what is meant by soft information. The reliability of a decoded bit is best described by the a-posteriori probability (APP) P(u|y). For an estimate of bit u(-1/+1) having received symbol y we define the *optimum soft output* as:

$$L(u) = \ln \frac{P(u = 1 | \mathbf{y})}{P(u = -1 | \mathbf{y})}$$

(2-5)

which is called the *log-likelihood ratio* (LLR). The LLR is a convenient measure since it encapsulates both soft and hard bit information in one number. The sign of the number corresponds to the hard decision while the magnitude gives a reliability estimate.

The LLR can be easily computed by noticing that a decoding algorithm that uses the maximum a-posteriori (MAP) rule inherently calculates the APPs required. In fact, once determined and used to choose the most likely bit, the APPs are discarded, throwing away useful information. MAP algorithms have been proposed by several authors [ChangH66] [AbendF70][BCJR74] but were generally ignored because the Viterbi algorithm can provide nearly identical hard outputs with less computational effort.

In this thesis, we will focus on the implementation of what we call the "forward-backward algorithm" of [ChangH66][BCJR74]. In the literature, this algorithm is often referred to as the MAP algorithm or the BCJR algorithm, which are both somewhat inaccurate names. Abend and Fritchman proposed a MAP decoder that is optimal under the constraint of fixed decoding delay [AbendF70]. A simplified suboptimal detector (SPS) based on the Abend and Fritchman algorithm was derived in [ErfanianP89]. The Abend and Fritchman type algorithm has the drawback that the complexity of the decoder is exponentially related to the fixed decision delay. In [LVS95] a MAP detector is derived that has linear dependence on the delay. In [Battail87] and [HagenauerH89] the soft-output Viterbi algorithm (SOVA) is derived. The SOVA has received a lot of attention lately due to its ease of implementation even though it provides suboptimal soft outputs. In our opinion, the forward-backward algorithm is a feasible alternative to SOVA especially when optimum soft outputs are required (for example in turbo decoders). The rest of this thesis is devoted to presenting architectures and examples of the practical application of the forward-backward algorithm.

### 2.2.2 Description of the Forward-Backward Algorithm

This description of the algorithm is based on [BCJR74] and [HOP96] to which the reader is referred to for a detailed derivation. The algorithm is based on the same trellis as the Viterbi algorithm. The algorithm is performed on a block of N received symbols which corresponds to a trellis with a finite number of stages N. We will choose the transmitted bit  $u_k$  from the set of  $\{-1,+1\}$ . Upon receiving the symbol  $y_k$  from the AWGN channel with noise variance  $\sigma^2$  we calculate the *branch probability* of the transition from state s' to state s as

$$\gamma_{\mathbf{k}}(\mathbf{s}',\mathbf{s}) = \exp\left(\frac{-1}{2\sigma^2} \|\mathbf{y}_{\mathbf{k}} - \mathbf{c}_{\mathbf{k}}(\mathbf{s}',\mathbf{s})\|^2\right)$$

(2-6)

where  $\mathbf{c}_{\mathbf{k}}(\mathbf{s}', \mathbf{s})$  is the expected symbol along the branch from state  $\mathbf{s}'$  to state  $\mathbf{s}$ .

The algorithm consists of three main steps:

• Forward Recursion. The *forward state probability* of being in each state of the trellis at each time k given the knowledge of all the previous received symbols is recursively calculated and stored:

$$\alpha_{k}(s) = \sum_{s'} (\alpha_{k-1}(s')\gamma_{k}(s',s)) \qquad k = 1...N-1$$

(2-7)

The recursion is initialized by forcing the starting state to state 0 and setting

$$\alpha_0(0) = 1$$

$\alpha_0(s) = 0 \qquad s \neq 0$

(2-8)

• **Backward Recursion**. The backward state probability of being in each state of the trellis at each time k given the knowledge of all the future received symbols is recursively calculated and stored:

$$\beta_{k-1}(s') = \sum_{s} (\beta_k(s)\gamma_k(s',s)) \qquad k = N...2$$

(2-9)

The recursion is initialized by forcing the ending state to state 0 and setting

$$\beta_{N}(0) = 1$$

$\beta_{N}(s) = 0 \qquad s \neq 0$

(2-10)

The trellis termination condition requires the entire block to be received before the backward recursion can begin.

• Log-Likelihood Ratio Calculation. The output LLR for each symbol at time k is calculated as

$$L(u_{k}) = \ln \frac{P(u_{k} = +1 | \mathbf{y}_{k})}{P(u_{k} = -1 | \mathbf{y}_{k})}$$

$$= \ln \frac{\sum_{\substack{(s',s) \\ u_{k} = +1}} \alpha_{k-1}(s')\gamma_{k}(s',s)\beta_{k}(s)}{\sum_{\substack{(s',s) \\ u_{k} = -1}} \alpha_{k-1}(s')\gamma_{k}(s',s)\beta_{k}(s)}$$

(2-11)

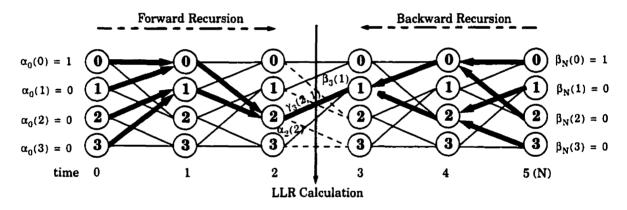

where the upper summation is over all branches with input label +1 and the lower summation is over all branches with input label -1. The procedure is depicted graphically in Fig. 2-7 for a short 5-stage trellis.

**Fig. 2-7:** Trellis processing in an N = 5 stage 4-state Forward-Backward algorithm corresponding to the encoder of Fig. 2-3. Shown is the calculation of one particular term in the lower summation of Equation 2-11. The terms in the upper summation are dashed while the terms in the lower summation are solid.

### 2.2.3 The Forward-Backward Algorithm in the Logarithmic Domain

The forward-backward algorithm was virtually ignored for many years because of the difficulty in implementing efficient exponentiation and multiplication. If the algorithm is implemented in the logarithmic domain like the Viterbi algorithm, then the multiplications become additions and the exponentials disappear. Addition is transformed according to the rule described in [KingsburyR71]. Following Erfanian and Pasupathy, who first applied this

rule to the Abend and Fritchman MAP algorithm [ErfanianP89], the additions are replaced using the Jacobi logarithm:

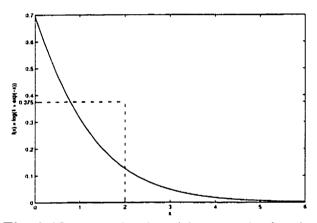

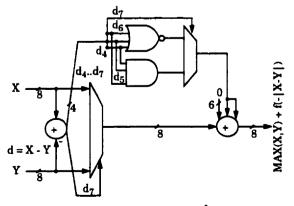

$$\ln(e^{X} + e^{Y}) = MAX(X, Y) + \ln(1 + e^{-|X - Y|})$$

= MAX<sup>\*</sup>(X, Y) (2-12)

which we call the MAX<sup>\*</sup> operation to denote that it is essentially a maximum operator adjusted by a correction factor. The second term, a function of the single variable X-Y, can be precalculated and stored in a small lookup table with negligible effects on performance [ErfanianP89].

The forward-backward algorithm will now be restated in the logarithmic domain. As with the Viterbi algorithm, logarithms of probabilities are referred to as *metrics*. Define the new quantities:

• Branch Metrics:

$$G_{k}(s', s) = \ln(\gamma_{k}(s', s))$$

(2-13)

• Forward State Metrics:

$$A_k(s) = \ln(\alpha_k(s)) \tag{2-14}$$

• Backward State Metrics:

$$B_k(s) = \ln(\beta_k(s)) \tag{2-15}$$

The branch metric calculation eliminates the exponential:

$$\mathbf{G}_{\mathbf{k}}(\mathbf{s}',\mathbf{s}) = \frac{-1}{2\sigma^2} \left\| \mathbf{y}_{\mathbf{k}} - \mathbf{c}_{\mathbf{k}}(\mathbf{s}',\mathbf{s}) \right\|^2$$

(2-16)

The forward state metric recursion becomes:

$$A_k(s) = MAX^* (A_{k-1}(s') + G_k(s', s))$$

$k = 1...N - 1$  (2-17)

with initial conditions:

$$\begin{aligned} \mathbf{A}_0(0) &= 0\\ \mathbf{A}_0(\mathbf{s}) &= -\infty \qquad \mathbf{s} \neq 0 \end{aligned} \tag{2-18}$$

The backward state metric recursion becomes:

$$B_{k-1}(s') = MAX_{s}^{*}(B_{k}(s) + G_{k}(s', s))$$

$k = N...2$  (2-19)

with initial conditions:

$$B_{N}(0) = 0$$

$$B_{N}(s) = -\infty \qquad s \neq 0$$

(2-20)

The dynamic range of the metrics is much lower than the associated probabilities. Since each probability has a value of less than or equal to one, each multiplication results in a smaller and smaller number. The metrics tend to grow much more slowly than the probabilities.

The output LLR becomes:

$$L(u_{k}) = \underset{\substack{(s',s)\\u_{k} = +1}}{MAX}^{*}(A_{k-1}(s') + G_{k}(s',s) + B_{k}(s)) - \underset{\substack{(s',s)\\u_{k} = -1}}{MAX}^{*}(A_{k-1}(s') + G_{k}(s',s) + B_{k}(s))$$

(2-21)

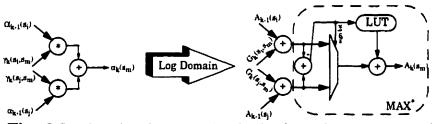

The computational kernel of the algorithm is now the MAX<sup>\*</sup> operation, which is analogous to the MIN operation in the Viterbi algorithm adjusted by a correction factor (see Fig. 2-8). If the correction factor is ignored then MAX<sup>\*</sup> reduces to MAX and the hard decisions are identical to those produced by the Viterbi algorithm and the soft decisions equivalent to those from the SOVA<sup>1</sup> [FBLH98].

Fig. 2-8: Log-domain processing in the forward recursive equation. Multiplications become additions and additions become the MAX operation. The shaded components are removed for the approximate algorithm.

### 2.3 The Sliding Window Forward-Backward Algorithm

The forward-backward algorithm as stated is a block processing algorithm. The constraint that the ending state be known implies that an entire block of data needs to be received before the backward recursion can begin. The memory requirements are therefore quite large. For a rate R code with memory length v ( $2^{v}$  states) and a block length of N, we have to store NR input words and  $2^{v}N$  forward state metrics so that they can be used during the

<sup>1.</sup> The SOVA proposed in [Battail87] has higher complexity than the algorithm proposed in [HagenauerH89].

backward recursion to calculate the LLRs. The branch metrics may require additional storage, or they may be recalculated as needed. The basic amount of storage required is therefore  $N(R+2^{v})$  words. Unfortunately, turbo codes, one of the most important applications, require large values of N for good performance. In addition, high-speed applications may not be able to tolerate the delays of block processing. To overcome these problems, a modification of the algorithm that operates over a small sliding window allows continuous processing with a fixed latency [DawidM95]. The idea is to relax the criterion that the ending state be known and to consider each ending state as equally likely. Viterbi makes a comparison with the Viterbi algorithm's ability to "start cold" in any state [Viterbi98]<sup>2</sup>. If the backward state probabilities are initialized to:

$$\beta_{\rm N}({\rm s}) = \frac{1}{2^{\rm v}} \qquad \forall {\rm s} \qquad (2-22)$$

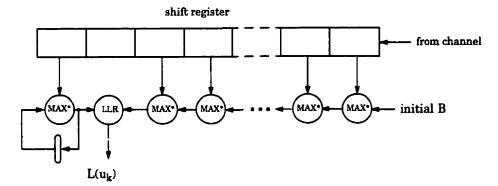

then after a *learning* or synchronization period the state probabilities (or metrics) will be as good as those calculated starting from a known ending state. A learning period of 6 memory lengths is usually enough to achieve nearly the performance of the optimal algorithm [Viterbi98]. The memory requirements are reduced to  $D_L+2$  words where  $D_L$  is the learning period. Fig. 2-9 shows the simplest form of the sliding window algorithm. The trade-off is that the new algorithm has to compute  $D_L$  backward stages for each decoded bit. A compromise between memory and computational complexity is given in [BDMP97] where the backward state metrics, determined by the learning recursion, are used to decode a block of  $M_b$  symbols. The structure of Fig. 2-9 which corresponds to  $M_b = 1$  is still useful in some applications due to its ease of implementation. An example is given in Chapter 4 that is simple enough to efficiently utilize this architecture.

The more efficient sliding window algorithm may be derived by dividing the backwards recursion into two distinct parts. First, a learning recursion of  $D_L$  steps is performed to generate reliable backward state metrics. The generated metrics are then used to decode a block of  $M_b = D_L$  symbols. The algorithm is best described by the time-space diagram in Fig. 2-10 introduced in [DawidM95] which divides the trellis into blocks of  $D_L$  stages. We will now describe the algorithm, referring to Fig. 2-10.

<sup>2.</sup> The Forward-Backward algorithm's recursive step is really just two Viterbi-like algorithms running in opposite directions with a slightly different computational kernel. In the case of the approximate algorithm, the kernels are identical.

**Fig. 2-9:** The log-domain sliding window Forward-Backward algorithm for  $M_b = 1$  [DawidM95]. The shaded boxes represent memory storage. The branch metric generators are not shown.

**Fig. 2-10:** Space-time diagram for the sliding window Forward-Backward algorithm with  $M_b = D_L$  [DawidM95]. The shaded areas represent the memory for the forward state metrics.

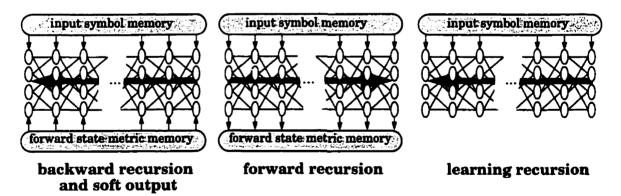

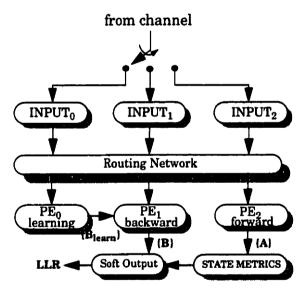

The algorithm begins once the first 2D<sub>L</sub> symbols have been received and stored in the input memory (not shown in the diagram). Let's consider what happens to a given stage of the trellis, say stage  $k + D_{L} + j$  where  $0 < j < D_{L}$ . If we draw a horizontal line across the diagram, it will cut through one of each kind of arrow, forward, backward and learning. Therefore, we see the progression through time. The stage is visited by the learning recursion, then the forward recursion and lastly the backward recursion. Then, in the next block of time, the forward recursion proceeds using the results of the learning recursion. The soft outputs are generated during the backward recursion, in reverse order<sup>3</sup>. The hardware requirements can be found by drawing a vertical line, say at time  $k + 3D_L + j$ ,  $0 < j < D_L$ . It can be seen that three recursion processors are required to run simultaneously, one each for the forward, backward, and learning recursions as shown in Fig. 2-11. Each processor consists of a branch metric generator,  $S = 2^{v} MAX^{*}$  units and the appropriate trellis routing along with S registers. The fully parallel structure ensures a throughput of 1 decoded bit/cycle after an initial latency of 4D<sub>L</sub>. The memory requirements for the forward state metrics can also be found this way. At any point after  $k + 3D_L$ , the state metric memory required will be  $D_L$  at any point in time. Therefore, the state metric memory requirements for a S state trellis are SD<sub>L</sub>. The structure of the decoder is shown in Fig. 2-12, which is derived from [DawidM95]. The input memory needs three independent banks, each of D symbols. The input symbols are directed to the correct branch metric generator (BMG) and then to the appropriate processing element (PE). A simplification in the soft output calculation may be obtained by noticing that the term  $B_k(s) + G_k(s', s)$  in Equation 2-21 has already been calculated by the backward recursion in Equation 2-19 and may be supplied directly to the soft output unit.

Fig. 2-11: A snapshot of computation in the trellis.

<sup>3.</sup> The outputs can be explicitly reversed using a LIFO. In a turbo decoder (Chapter 3), the forward-backward algorithm is followed by an interleaver which can perform the reversal for free.

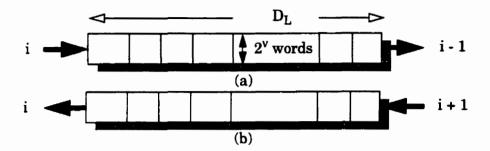

The structure of the four memory banks and the memory access schedule remains to be defined. We will start with the forward state metric memory. Referring to Fig. 2-10, the forward recursion writes state metrics to the state metric memory that are read out in the opposite order by the soft output unit during the next time block. Since the overall memory requirements are never greater than  $D_L$  sets of state metrics, a S x  $D_L$  dual-port memory can be used to implement a bi-directional shift register (Fig. 2-13). To maintain proper shift register operation, the read operation should complete before the contents of the memory address are overwritten. The direction of the shifting should be reversed every  $D_L$  time steps.

The input buffers are each  $D_L$  rows long, but the width depends on the code rate R. For example, a rate R = 1/2 code requires three (2 word x  $D_L$ ) buffers. In addition to the case where data is read and then replaced by new data like the state metric memory a non-destructive read is necessary. If an actual shift register is used instead of dual-port RAM, then a feedback path should be added to create a circular bi-directional buffer as shown in Fig. 2-14.

Fig. 2-12: Architecture of the sliding-window Forward-Backward algorithm with  $M_b=D_L$  (derived from [DawidM95])

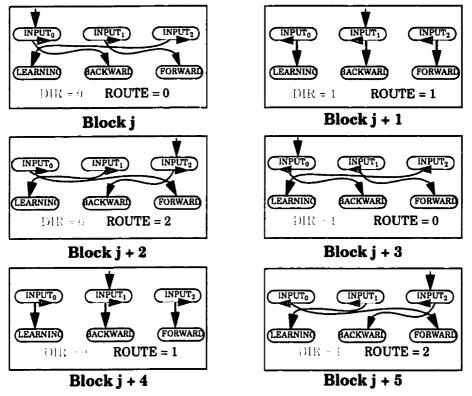

The input buffer access schedule may be derived by considering the configuration of the architecture for each block of  $D_L$  clock ticks. During any given block, one buffer is selected to write to (destructive write), and two are operating in the cyclic reading mode. The direction of the accesses for each buffer reverses every  $D_L$  clock ticks. Finally, we see that there are three different routings from input buffer to processing element. The cycle of the six distinct combinations is shown in Fig. 2-16. From this figure, the control signals can be defined. We

Fig. 2-13: Implementing the forward state metric memory with a bidirectional shift register. In (a) results from trellis block i are stored while results from the previous block i - 1 are sent to the soft output unit. In (b) results from block i + 1 are stored while the previously stored block i is read out in the opposite order in which it was written.

**Fig. 2-14:** Logical operation of the input buffers. The shift register is reversible in direction and either writes new data, destroying the old contents or is cyclic. A dual-port RAM implementation would not explicitly need the feedback.

note that the direction control is also used to control the forward state metric memory. The overall period of six is a product of the periods of the following two control signals:

- The direction signal DIR with a period of 2.

- The routing signal ROUTE, which controls both the input switch and routing network. ROUTE has a period of 3.

The algorithm is described by the pseudo-code in Fig. 2-15:

```

{A} := initial_A_values;

for j := 0 to \infty do

{B} := {B_{learn}}

{B<sub>learn</sub>} := initial_B_values;

DIR := j \mod 2;

ROUTE := j \mod 3;

for \mathbf{k} = (\mathbf{j}\mathbf{D}_{L} + 1) to ((\mathbf{j} + 1)\mathbf{D}_{L}) do simultaneously

if (DIR = 0) then

INPUT_{ROUTE}[(j + 1)D_{L} - k + 1] := received_symbol[k];

\{\mathbf{B}_{\text{learn}}\} := \text{smg}(\{\mathbf{B}_{\text{learn}}\}, \text{bmg}(\text{INPUT}_{(\text{ROUTE} + 2) \mod 3}[k - jD_L]));

\{\mathbf{B}\} := \operatorname{smg}(\{\mathbf{B}\}, \operatorname{bmg}(\operatorname{INPUT}_{\operatorname{ROUTE}}[\mathbf{k} - j\mathbf{D}_{\mathbf{L}}]));

\{A\} := SM_MEM[(j + 1)D_{L} + 1] := smg(\{A\}, bmg(INPUT_{(ROUTE + 1) mod 3}[k - jD_{L}]));

LLR := soft_output((B), bmg(INPUT<sub>ROUTE</sub> [k - jD<sub>L</sub>]), SM_MEM[(j+1)D<sub>L</sub> - k + 1]);

else

INPUT<sub>ROUTE</sub>[k - jD<sub>L</sub>] := received_symbol[k];

\{\mathbf{B}_{\text{learn}}\} := \text{smg}(\{\mathbf{B}_{\text{learn}}\}, \text{bmg}(\text{INPUT}_{(\text{ROUTE} + 2) \mod 3}[(j+1)D_{L} \cdot k + 1]));

\{\mathbf{B}\} := \operatorname{smg}(\{\mathbf{B}\}, \operatorname{bmg}(\operatorname{INPUT}_{\operatorname{ROUTE}} [(j+1)D_{L} - k + 1]));

(A) := SM_MEM[k - jD_L] := smg((A), bmg(INPUT_{(ROUTE + 1) mod 3}[(j+1)D_L - k + 1]));

LLR := soft_output(\{B\}, bmg(INPUT_{ROUTE} [(j+1)D_L - k + 1]), SM_MEM[k - jD_L]);

end if;

end for;

end for;

```

**Fig. 2-15:** Pseudo-code for the sliding window algorithm. {A} are the forward state metrics, {B} are the backward state metrics and  $\{B_{learn}\}$  are the backward state metrics in the learning recursion. The state metric processing elements are represented by smg() and the branch metric generators by bmg(). The soft output unit is represented by soft\_output(). The forward state metrics are stored in SM\_MEM. The soft output is LLR. Two assignment operators (:=) on the same line imply simultaneous assignment.

Fig. 2-16: The cyclic memory access sequence. The values of the control signals DIR and ROUTE are indicated. j= 0,6,12,...

### 2.4 Summary

In this chapter we have reviewed the basic theory of the forward-backward algorithm, which will be necessary for the rest of this thesis. The main points of this chapter are:

- The forward-backward algorithm is an algorithm for detecting a noisy signal in the presence of intersymbol interference (ISI) or decoding a convolutional code.

- The forward-backward algorithm provides optimum soft outputs, a measure of the decoding reliability.

- The main components of the forward-backward algorithm are a forward recursion, a backward recursion, and soft output calculation.

- The computational complexity can be reduced by working in the logarithmic domain.

- In the log-domain the recursions are just like the recursion in the Viterbi algorithm adjusted by a correction factor that is stored in a small lookup table.

- The sliding-window algorithm can be used to reduce the memory requirements and provide continuous decoding with a fixed delay.

Chapter

## Implementation of a Turbo Decoder

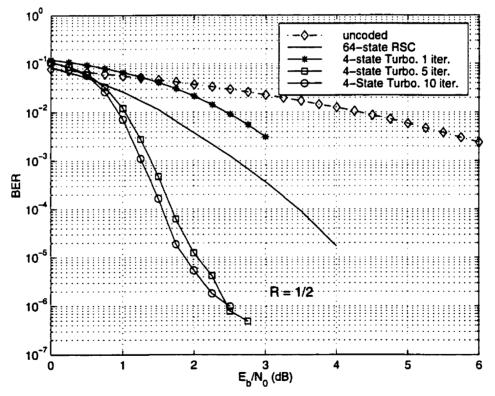

Turbo codes, the best known error-correcting codes, use the forward-backward algorithm as the main component of their decoding algorithm. In addition to their near-optimum performance, turbo codes are relatively simple to decode. In this chapter, we describe the design of TORBO-TM2, an FPGA implementation of a turbo decoder on the Transmogrifier-2 reconfigurable system. In Section 3.1 we review the basic theory of turbo codes and their decoding algorithm. Section 3.2 is a survey of the existing turbo decoder implementations. In Section 3.3 we present the design of a general turbo decoder for hardware implementation. Section 3.4 describes the design of TORBO-TM2. Finally, Section 3.5 is a review of the main points and contributions of this chapter.

### 3.1 Turbo Codes

### 3.1.1 Concatenated Codes

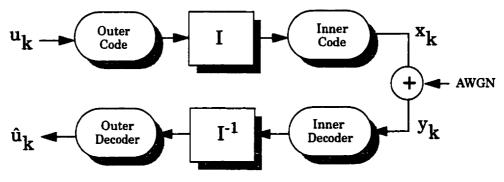

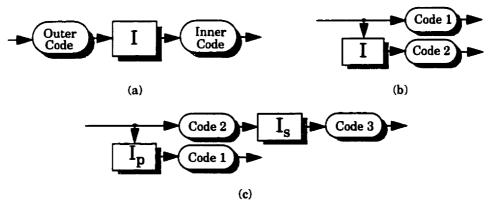

Concatenated codes were introduced by Forney in [Forney66] as a way of combining the power of two relatively simple codes. The classic example of a concatenated code is the serial concatenated code shown in Fig. 3-1. The code is constructed by concatenating an inner and an outer code separated by an interleaver. The decoder is a mirror image of the encoder. The results of the inner decoder are deinterleaved and used as inputs to the outer decoder. The purpose of the interleaver/de-interleaver pair is to spread any errors caused by burst noise to make them appear as random error events. One popular technique is to use an inner Reed-Solomon code to correct the output of the convolutional code which typically contains burst errors. The advantage of a concatenated technique is that the combined complexity of the component decoders is less than that of a decoder for a single code with comparable performance.

**Fig. 3-1:** A serial concatenated encoder and decoder. The interleaver is denoted by I and the deinterleaver by I<sup>-1</sup>.

In recent years, the ideas behind concatenated codes have been extended and improved greatly. The two new ideas are:

- Soft decoding: Soft reliability information is exchanged between the decoders instead of hard bit decisions. Performance improves as the inner decoder has more information to work with.

- **Iterative decoding**: Instead of separately decoding the inner and outer codes, the decoder considers the combined code. Maximum likelihood decoding of the joint code is too complex because of the interleaver, so a heuristic *iterative* technique is used instead.

The three main categories of concatenated codes are serial [BDMP96], parallel [BGT93] and hybrid (both serial and parallel) [DivsalarP97] codes as shown in Fig. 3-2. Although parallel

Fig. 3-2: Classes of concatenated codes. (a) Serial. (b) Parallel. (c) Hybrid

codes have been shown to achieve the performance closest to the Shannon limit they are outperformed by serial codes at very low bit error rates  $(10^{-7} \text{ or below})$  [BDMP96].

#### 3.1.2 Encoders for Turbo Codes